S & M 1888

# Simulation on Junctionless Silicon Nanowire Devices for Implementation of Photodetection Circuit in Retinal Prosthesis

Sangmin Lee\*

Department of Biomedical Engineering, Kyung Hee University, Yongin, Gyeonggi 17104, Republic of Korea

(Received April 25, 2018; accepted March 20, 2019)

*Keywords:* neural stimulation, silicon nanowire device simulation, photodetection circuit, retinal prosthetic system

Semiconductor nanowires have been studied owing to their excellent electrical properties. To implement an integrated system based on nanowires, well-aligned arrays of a nanowire are required for scalable and repeatable fabrication. In our previous results, a comparative study based on the current conduction mechanism of junctionless silicon nanowires was performed, and their characteristics were analyzed to offer a design guideline. Also, to implement a silicon-nanowire-based device, a top-down, wafer-level fabrication process of silicon-nanowire arrays on a flexible substrate was reported. The fabricated device consists of a voltage divider and a current driver in which silicon nanowires are used as a photodetector (PD) and fieldeffect transistors (FETs). The implemented silicon-nanowire-based circuit detects external light, generating a stimulation signal in proportion to the light intensity and transmitting the signal to a microelectrode. In this study, an analytical model based on a conduction mechanism of junctionless silicon nanowires is verified using a three-dimensional device simulator. Also, by applying the extracted electrical parameters of silicon-nanowire-based devices, the proposed photodetection circuit is simulated for the implementation of a photosensitive retinal prosthetic device. The results of this study can be applied to address novel silicon-nanowire-based neural stimulation devices and to guide the design of a high-resolution retinal prosthetic system.

## 1. Introduction

In the human eye, photoreceptor cells sense light and convert it into electrical signals that then stimulate optic nerves in the brain. The degeneration of the photoreceptors produces visual disorders such as retinitis pigmentosa (RP) and age-related macular degeneration (AMD), which affects more than 15 million people throughout the world. (1-3) Nevertheless, effective medical treatment methods for such diseases are not available. Even though the blind has irrecoverable photoreceptor degeneration, 78.4% of bipolar and 29.7% of retinal ganglion cells (RGCs) are still alive to transmit neural impulses. (4,5) Thus, through the electrical stimulation of the remaining neural network, vision can be restored.

\*Corresponding author: e-mail: sangmlee@khu.ac.kr https://doi.org/10.18494/SAM.2019.2286

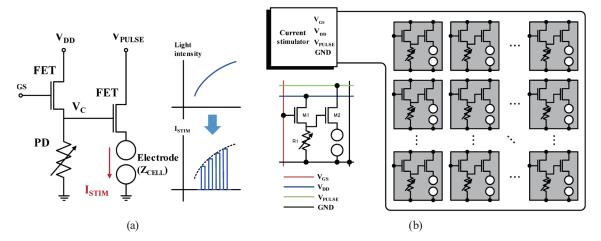

Several research groups worldwide have attempted to use electrical signals modulated by visual data obtained from external image acquisition devices. (6-8) For other approaches, integrating a solid-state photodiode into a microelectrode array (MEA) has been proposed. (9) For those devices, photodiodes are integrated with signal amplification circuits to increase and control the magnitudes of stimulation current at low light intensities. In our previous report, we have proposed light-responsive silicon-nanowire photodetectors (PDs) on a flexible substrate, which can convert visible light into electrical signals. (10) In the report, the devices using a topdown fabrication method have shown excellent potential for applications in retinal prosthetic systems with high photosensitivity, photoresponsivity, and mechanical flexibility. However, the proposed scheme generated insufficient photocurrents to stimulate RGCs, and the amplitude of the stimulation current had to be amplified. To achieve a sufficient current stimulus, a transimpedance amplifier has been integrated with silicon-nanowire PDs. (11,12) Despite the recent results, there remain problems to be resolved, such as the protection of electrodes from excessive charge injection, the avoidance of charge spreading due to a high-amplitude current stimulus, and cell necrosis due to the overheating of stimulator chips. Therefore, research on a gain-controllable scheme using silicon-nanowire devices to protect RGCs and electrodes is necessary. The gain-controllable scheme of the retinal prosthetic system using the siliconnanowire-based photodetection circuit is shown in Fig. 1. The proposed method consists of a voltage divider and a current driver, and is implemented using silicon-nanowire PDs, siliconnanowire field-effect transistors (FETs), and a microelectrode on a flexible substrate. The voltage divider with series-connected silicon-nanowire PD and FET generates control voltage  $(V_C)$ owing to the resistance variation from the external light intensity to the silicon-nanowire PD. In the current driver, where the silicon-nanowire FET and microelectrodes are connected in series, the current stimulus pulses can be delivered to the microelectrode by the amplitude-modulated driving current, which is proportional to the external light intensity.

Fig. 1. (Color online) Schematic. (a) Operation of photodetection circuit. (b) Schematic of the PD-based retinal prosthetic system.

Although there has been much research on the development of various fabrication processes, few studies on the channel conduction mechanism and theoretical modeling have been conducted on top-down fabricated silicon nanowires. In this paper, an analytical model based on the conduction mechanism of junctionless silicon nanowires is verified using a three-dimensional device simulator. Also, by applying the extracted electrical parameters of siliconnanowire-based devices, the proposed photodetection circuit is simulated for implementation in a photosensitive retinal prosthetic device.

### 2. Methods

### 2.1 Fabrication method

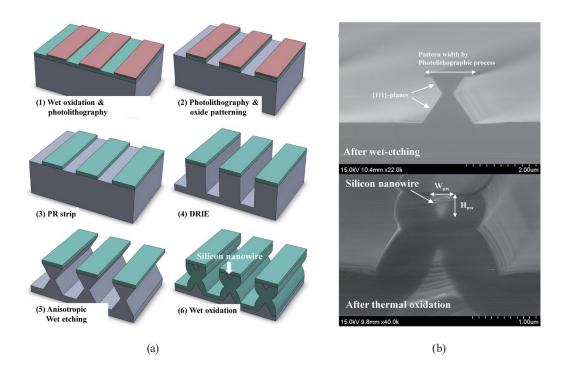

To derive the drain current conduction mechanism of the proposed silicon-nanowire device, the top-down fabrication process is described to explain the cross-sectional structure of the silicon nanowire. The top-down fabrication processes of the (100)-silicon-nanowire array are shown in Fig. 2(a). The silicon nanowires are fabricated using a p-type, 4 inch, single-crystalline silicon wafer. For the fabrication process using (100)-oriented silicon, a 1000-Å-thick thermal oxide layer is grown on the silicon substrate by wet oxidation. After line and space patterns are defined by photolithography and dielectric etching, photoresists

Fig. 2. (Color online) Fabrication. (a) Top-down process of (100) silicon nanowire. (b) Cross-sectional structure of (100) silicon nanowire.

are removed by O<sub>2</sub> plasma ashing. Then, rectangular silicon columns are fabricated by silicon deep-reactive-ion etching (DRIE). Subsequently, anisotropic silicon wet etching using tetramethyl-ammoniumhydroxide (TMAH) solution is performed for 90 s. The exposed silicon surface is etched by exploiting the anisotropic wet etching properties of silicon in TMAH solution. After the fabrication of hourglass-shaped silicon structures, the silicon nanowire array is fabricated by thermal oxidation, which produces silicon dioxide from a chemical reaction between silicon and oxygen.

The fabrication results of the arrayed silicon nanowire are shown in Fig. 2(b). As shown in the figure, the height of the silicon nanowire ( $H_{nw}$ ) is determined by the photolithographic pattern width, which is an inherent property of the (100)-single-crystalline-silicon wafer. The width of the silicon nanowire ( $W_{nw}$ ) is precisely controlled by adjusting the processing time of the thermal oxidation process. The amount of drain current mostly depends on the accumulation current through the surface of the silicon nanowire, which can be increased by increasing the pattern width in the photolithographic process. However, increasing the pattern width results in increased  $H_{nw}$ , which needs to be minimized to achieve a high current on/off ratio and low power consumption. Therefore, for enhanced device characteristics, increasing the number of silicon nanowires is necessary.

#### 2.2 Current conduction model of silicon nanowires

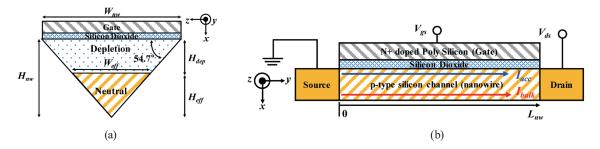

To understand the operation mechanism of the silicon-nanowire FET, a quantitative current conduction model based on semiconductor theory is used. (14) As illustrated in Fig. 3(a), the cross section of (100)-silicon nanowires can be assumed to have a triangular shape. The source and drain are assumed to be  $P^+$ -doped, and the silicon nanowire is assumed to have a p-type channel. The gate material is  $N^+$ -doped polysilicon and is assumed to be uniform. As shown in Fig. 2(b), the drain current of the proposed p-type silicon nanowire consists of two components, hole accumulation current ( $I_{acc}$ ) and bulk current ( $I_{bulk}$ ). The total drain current in the device is given by the sum of the current in the accumulation channel and the current in the bulk of the device.

The proposed device is normally turned off; therefore, when zero bias is applied to the gate, the channel is fully depleted. From the gradual channel approximation, the hole accumulation current ( $I_{acc}$ ) in the channel can be expressed as

Fig. 3. (Color online) Schematic of silicon-nanowire device for quantitative analysis. (a) Cross-sectional view. (b) Lateral view.

$$I_{acc} = \mu_s \cdot \frac{W_{nw}}{L_{nw}} \cdot C_{ox} \cdot \int_0^{V_{ds}} \left( \left( V_{gs} - V_{fb} \right) - V_{cs} \right) \cdot dV_{cs} , \qquad (1)$$

where  $\mu_s$  is the hole surface mobility,  $L_{nw}$  is the length of the silicon nanowire,  $W_{nw}$  is the width of the silicon nanowire,  $C_{ox}$  is the gate oxide capacitance per unit area,  $V_{ds}$  is the bias voltage,  $V_{gs}$  is the gate-source voltage,  $V_{fb}$  is the flat-band voltage, and  $V_{cs}$  is the local potential along the silicon-nanowire channel. The bulk current  $(I_{bulk})$  occurs when a nondepleted silicon region exists below the channel. When the voltage applied to the gate exceeds the flat-band voltage, the silicon-nanowire channel is fully depleted. Therefore, as illustrated in Fig. 3(a), the cross sections of arbitrary points along the silicon nanowire can be assumed to be a depletion region in the channel and a neutral region below the channel. The gate depletion height can be derived from solving the one-dimensional Poisson's equation. The bulk current in the neutral region  $(I_{bulk})$  can be derived using the gradual channel approximation as

$$dR = \frac{1}{q \cdot N_A \cdot \mu_b} \cdot \frac{dy}{A_{eff}} = \frac{1}{q \cdot N_A \cdot \mu_b} \cdot \frac{dy}{\frac{1}{2} W_{eff} \cdot H_{eff}} = \frac{1}{q \cdot N_A \cdot \mu_b} \cdot \frac{\tan 54.7^{\circ}}{H_{eff}^{2}} dy,$$

$$I_{bulk} \cdot dy = q \cdot N_A \cdot \mu_b \cdot \frac{1}{2} W_{eff} \cdot H_{eff} \cdot dV_{cs} = q \cdot N_A \cdot \mu_b \cdot \frac{H_{eff}^{2}}{\tan 54.7^{\circ}} \cdot dV_{cs},$$

$$I_{bulk} \cdot \int_{0}^{L_{nw}} dy = \frac{q \cdot N_A \cdot \mu_b}{\tan 54.7^{\circ}} \int H_{eff}^{2} \cdot dV_{cs},$$

$$I_{bulk} = \frac{q \cdot N_A \cdot \mu_b}{L_{nw} \cdot \tan 54.7^{\circ}} \int (H_{nw} - H_{dep})^{2} \cdot dV_{cs},$$

$$(2)$$

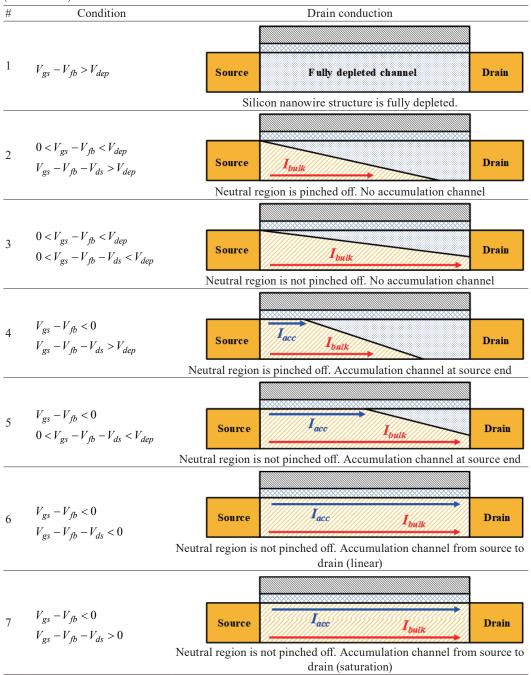

where q is the elementary charge,  $N_A$  is the acceptor doping concentration,  $\mu_b$  is the bulk mobility,  $A_{eff}$  is the area of the neutral region,  $W_{eff}$  is the width of the neutral region,  $H_{eff}$  is the height of the neutral region,  $H_{nw}$  is the height of the nanowire, and  $H_{dep}$  is the depletion height. From the fabrication process of (100)-silicon nanowires, the angle of the (111)-planes of the structure is 54.7°, which means that  $H_{nw}$  depends on  $W_{nw}$ . The summarized result of the quantitative drain current due to the integration range of  $V_{cs}$  is shown in Table 1. As shown in the table, the detailed drain current conduction mechanism can be distinguished in seven cases due to the applied gate voltage.

## 3. Results

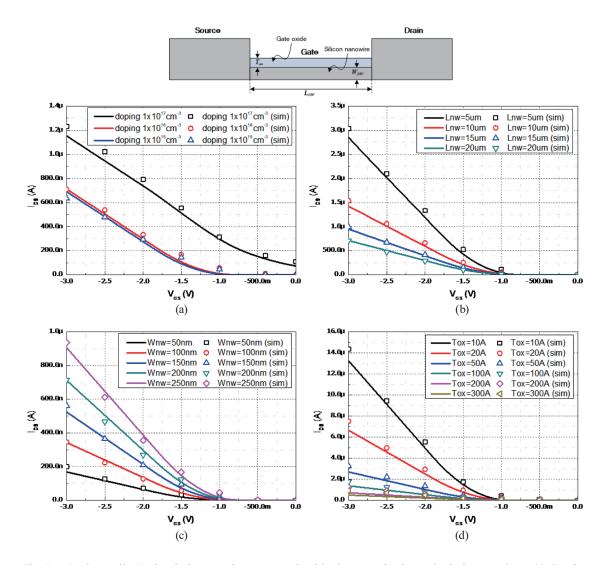

To determine the electrical characteristics of the silicon-nanowire device, such as maximum on-current and current on/off ratio, the device simulation tool SENTAURUS (Synopsys, USA) is used. The drain current due to applied gate voltage is simulated for acceptor doping concentrations of  $1 \times 10^{16}$ ,  $1 \times 10^{17}$ , and  $1 \times 10^{18}$  cm<sup>-3</sup>, which have resistivities of approximately 1, 0.1, and 0.01  $\Omega$ ·cm, respectively [Fig. 4(a)]. Also, simulation results of the drain currents

Table 1 (Color online) Summarized drain current conduction mechanism.

from the variations in the length of the silicon nanowire (5, 10, 15, and 20 mm), the width of the silicon nanowire (50, 100, 150, 200, and 250 nm), and gate oxide thickness (10, 20, 50, 100, 200, and 300 Å) are shown in Figs. 4(b)–4(d), respectively. The applied bias voltage ( $V_{ds}$ ) is –3 V, and the gate voltage ( $V_{gs}$ ) is applied from –3 to 0 V. During the drain current simulation, each parameter is fixed except the input parameter ( $N_A$  fixed to 1 × 10<sup>17</sup> cm<sup>-3</sup>,  $L_{nw}$  fixed to 20 mm,

Fig. 4. (Color online) Simulation results compared with the quantitative calculation results. (a) Doping concentration. (b) Length of silicon nanowire. (c) Width of silicon nanowire. (d) Gate oxide thickness.

$W_{nw}$  fixed to 200 nm, and  $T_{ox}$  fixed to 200 Å). In Table 2, the parameters for the drain current conduction model analysis of silicon nanowires for simulation and calculation are summarized. The compared results of device simulation using SENTAURUS and the quantitative analysis calculation are similar, indicating that the drain conduction mechanism of the silicon nanowire can be used for the parameterization of the silicon-nanowire devices.

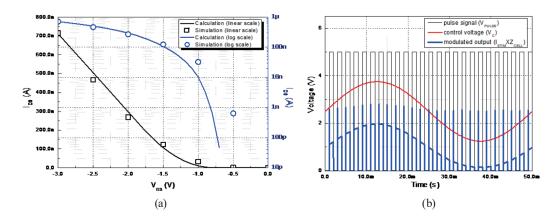

From the results, the values of  $L_{nw}$ ,  $W_{nw}$ ,  $T_{ox}$ , and  $N_A$  are determined to be 20 µm, 200 nm, 200 Å, and  $1 \times 10^{17}$  cm<sup>-3</sup>, respectively. The dimensions are derived by mainly considering the off-current level, which should be minimized, because of the unnecessary power dissipation. The simulation result for the above conditions is plotted in Fig. 5(a), where the maximum oncurrent and current on/off ratio for a single silicon nanowire are approximately 700 nA and

$cm^2/(V \cdot s)$

Hole bulk mobility ( $\mu_b$ )

| Summarized parameters for drain current cond                    | duction inoder analysis of since               | m nanowne.         |

|-----------------------------------------------------------------|------------------------------------------------|--------------------|

| Parameter                                                       | Value                                          | Unit               |

| Silicon band gap $(E_g)$                                        | 1.12                                           | eV                 |

| Intrinsic carrier concentration $(n_i)$                         | $1.50 \times 10^{10}$                          | $\mathrm{cm}^{-3}$ |

| Boltzmann's constant (k)                                        | $1.38 \times 10^{10}$                          | $J \cdot K^{-1}$   |

| Absolute temperature $(T)$                                      | 300                                            | K                  |

| Elementary charge (q)                                           | $1.60 \times 10^{10}$                          | C                  |

| Absolute permittivity ( $\varepsilon_0$ )                       | $8.85 \times 10^{10}$                          | F/m                |

| Relative permittivity of silicon dioxide ( $\varepsilon_{ox}$ ) | 3.9                                            |                    |

| Relative permittivity of silicon ( $\varepsilon_{si}$ )         | 11.7                                           |                    |

| Nanowire width $(W_{nw})$                                       | $300 \times 10^{-9}$                           | m                  |

| Nanowire height ( $H_{nw}$ )                                    | $H_{nw} = (W_{nw}/2) \times \tan 54.7^{\circ}$ | m                  |

| Nanowire length ( $L_{nw}$ )                                    | $20 \times 10^{-6}$                            | m                  |

| Hole surface mobility $(\mu_s)$                                 | 240                                            | $cm^2/(V \cdot s)$ |

|                                                                 |                                                |                    |

Table 2

Summarized parameters for drain current conduction model analysis of silicon nanowire

458

Fig. 5. (Color online) (a) Results of silicon-nanowire device for gain-controllable scheme. (b) Verification of gain-controllable protocol using the silicon-nanowire-based retinal prosthetic system.

$1 \times 10^3$ , respectively. From the simulation result, increasing the number of silicon nanowires for device fabrication is necessary to drive sufficient current to stimulate retinal cells. Therefore, a fabrication process using a top-down method to achieve a highly densified silicon-nanowire array has many advantages compared with a bottom-up approach. Using the parameters of the silicon-nanowire FET, a circuit analysis tool [OrCAD PSpice Designer Lite (Cadence Design Systems, Inc., USA)] is used to verify the gain-controllable scheme. As shown in Fig. 5(b), the control voltage ( $V_C$ ) is generated by the resistance variation of the silicon-nanowire PD due to external light intensity. Also, the current stimulus ( $I_{STIM}$ ) is modulated with a pulse signal ( $V_{PULSE}$ ) for amplification.

## 4. Conclusion

In this paper, a simplified and gain-controllable retinal prosthetic device with photosensitive silicon-nanowire PDs integrated with silicon-nanowire FETs is presented. An analytical model based on a conduction mechanism of junctionless silicon nanowires is verified using a three-dimensional device simulator. Also, by applying the extracted electrical parameters of the silicon-nanowire-based devices, the proposed photodetection circuit is simulated for implementation in a photosensitive retinal prosthetic device. The results are promising, with the current stimulus sufficiently amplified and controlled to evoke neural impulses. The results in this paper can be applied to a novel silicon-nanowire-based neural stimulation device and to guide the design of a high-resolution retinal prosthetic system.

# Acknowledgments

This work was supported by National Research Foundation of Korea (NRF) grants funded by the Korean government (MSIP; Ministry of Science, ICT, & Future Planning (No, NRF-2017R1C1B5017561).

#### References

- 1 E. L. Berson: Proc. Natl. Acad. Sci. U.S.A. 93 (1996) 4526.

- 2 D. S. Friedman, B. J. O'Colmain, B. Munoz, S. C. Tomany, C. McCarthy, P. T. de Jong, B. Nemesure, P. Mitchell, J. Kempen, and N. Congdon: Arch. Ophthalmol. 122 (2004) 564.

- 3 W. Mokwa: Proc. 16th Int. Solid-State Sens., Actuators, Microsyst., Conf. (2011) 2825–2830.

- 4 J. L. Stone, W. E. Barlow, M. S. Humayun, E. de Juan Jr., and A. H. Milam: Arch. Ophthalmol. 110 (1992) 1634.

- 5 S. Y. Kim, S. Sadda, J. Pearlman, M. S. Humayun, E. de Juan Jr., B. M. Melia, and W. R. Green: Retina 22 (1992) 471.

- 6 M. Humayun, J. D. Dorn, L. Cruz, G. Dagnelie, J. Sahel, P. Stanga, A. V. Cideciyan, J. Duncan, D. Eliott, E. Filley, A. Ho, A. Santos, A. Safran, A. Arditi, L. Priore, and R. Greenberg: Ophthalmology 119 (2012) 779.

- 7 K. Chen, Z. Yang, L. Hoang, J. Weiland, M. Humayun, and W. Liu: IEEE J. Solid-State Circuits 45 (2010) 1946.

- 8 J. Rizzo: J. Neuroophthalmol. 31 (2011) 160.

- 9 E. Zrenner, K. Bartz-Schmidt, H. Benav, D. Besch, A. Bruckmann, V. Gabel, F. Gekeler, U. Greppmaier, A. Harscher, S. Kibbel, J. Koch, A. Kusnyerik, T. Peters, K. Stingl, H. Sachs, A. Stett, P. Szurman, B. Wilhelm, and R. Wilke: Proc. R. Soc. B 278 (2011) 1489. https://doi.org/10.1098/rspb.2010.1747

- 10 S. Lee, S. Jung, S. Park, J. Ahn, S. Hong, H. Yoo, M. Lee, and D. Cho: Sens. Mater. 24 (2012) 205.

- 11 S. Lee: Microsyst. Technol. 23 (2017) 491.

- 12 S. Lim, H. Kim, C. Seok, H. Song, S. Lee, S. Jung, H. Yoo, S. Oh, J. Ahn, K. Koo, D. Cho, and H. Ko: J. Comput. Theor. Nanosc. 12 (2015) 769.

- 13 S. Lee and D. Cho: Microelectron. Eng. 175 (2017) 23.

- 14 J.-P. Colinge: Silicon-on-Insulator Technology: Materials to VLSI (Springer, Heidelberg, 2004).

## **About the Author**

Sangmin Lee received his B.S. and Ph.D. degrees from the School of Electrical Engineering, Seoul National University, Republic of Korea, in 2005 and 2013, respectively. From 2013 to 2016, he worked as a research staff member at Samsung Advanced Institute of Technology (SAIT), Samsung Electronics, Inc. In 2016, he joined the Department of Biomedical Engineering, Kyung Hee University, Yongin, Republic of Korea, where he is currently an assistant professor. His main research interest is in biomedical sensors and systems for application in Internet of Things (IoT) devices.