S & M 1152

# Variable-Dynamic-Range Complementary Metal-Oxide-Semiconductor Image Sensor with Gate/Body-Tied Metal Oxide Silicon Field Effect Transistor-Type Photodetector Using Feedback Structure

Myunghan Bae, Sung-Hyun Jo, Byung-Soo Choi, Hee Ho Lee, Pyung Choi, and Jang-Kyoo Shin\*

School of Electronics Engineering, Kyungpook National University, 80 Daehak-ro, Buk-gu, Daegu 702-701, Korea

(Received March 30, 2015; accepted September 7, 2015)

Keywords: CMOS image sensor, gate/body-tied PMOSFET, dynamic range, feedback structure

In this paper, a new pixel structure for wide-dynamic-range imaging applications is proposed using a feedback mechanism. The pixel is based on a 3-transistor (3-Tr) active pixel sensor (APS) with a gate/body-tied (GBT) p-channel metal—oxide—silicon field-effect transistor (PMOSFET)-based photodetector. The proposed APS is designed and fabricated using a 0.35 µm 2-poly 4-metal standard complementary metal—oxide—semiconductor (CMOS) technology, and its characteristics are simulated and measured. The pixel consists of a conventional 3-Tr APS with a GBT photodetector and an additional NMOSFET switch. The GBT photodetector is formed using a PMOSFET with a floating gate connected to an n-well and a transfer gate. The new pixel has a tunable dynamic range achieved by adjusting the applied reference voltage level and its duration. Although the pixel size is increased by 69%, the dynamic range is significantly extended to a maximum of 360% by feedback of the output voltage of each pixel.

#### 1. Introduction

Complementary metal—oxide—semiconductor (CMOS) devices are gradually taking over charge-coupled devices (CCDs) in the image sensor market owing to their advantages of high integration and low power dissipation. For the imaging markets, such as in automotive and surveillance applications, a wide dynamic range (WDR) is one of the most important performance requirements of the CMOS image sensor (CIS) to capture a scene without any loss of information even under extreme illumination conditions.<sup>(1-6)</sup>

To overcome these issues, several on-chip techniques that can extend the dynamic range of an image sensor have been proposed.<sup>(7–10)</sup> The multi-integration technique is currently the most commonly used approach at the industrial level, because it is based on a simple concept. Moreover, this approach is easily implementable with a CMOS sensor. The main disadvantage of this method is the cost of the processing needed to synthesize the final image. The simplest approach is the logarithmic technique. This case results in a logarithmic relationship between the light intensity

\*Corresponding author: e-mail: jkshin@ee.knu.ac.kr

input and the voltage output covering more than six decades of light intensity. The main advantages of this technique are its simple architecture and WDR. On the other hand, poor response at low light intensity and high residual fixed pattern noise (FPN) are the main drawbacks. Another method is to use both linear response and logarithmic response. (11,12) Lin-log pixel operates in the linear mode under the low illumination condition, like conventional active pixel sensors (APSs). In the logarithmic mode or under the high illumination condition, the pixel has low sensitivity. On the basis of the operating conditions, the lin-log pixel exhibits a very wide dynamic range compared with the conventional pixel. However, the lin-log pixel requires additional architectures and control signals to operate in the logarithmic mode.

In our previous research, to extend a new pixel's dynamic range, an additional photodetector was incorporated into the pixel structure along with the NMOSFET switch. Also, we successfully demonstrated a new pixel structure and its successful operation for improving the dynamic range under the fixed bias condition of a transfer gate. (13–16) We presented a pixel that can be switched between two operating modes depending on the transfer gate voltage, namely, normal mode and WDR mode. It has only two dynamic range values depending on the operation mode (28 dB for the normal mode and 98 dB for the WDR mode).

In this work, a new pixel structure based on a 3-Tr APS structure using a gate/body-tied (GBT) photodetector is proposed and implemented; its dynamic range can be controlled by adjusting the duration of application as well as the level of the reference voltage. As a result, the proposed pixel has various dynamic ranges according to the reference voltage. The details of the pixel structure and performance characteristics of the proposed APS are discussed in the following sections.

# 2. Operational Principle

# 2.1 Design of proposed APS

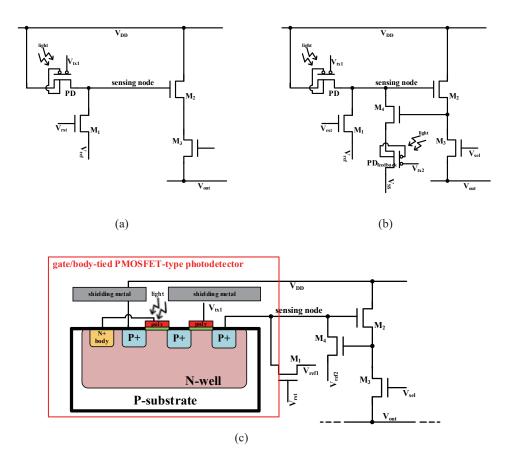

Figure 1 shows the schematic diagrams of the previous WDR APS and proposed APS. The conventional APS with a GBT photodetector is illustrated in Fig. 1(a). The structure of the previous WDR APS was that the sensing node of the conventional APS with a GBT photodetector is connected to an additional GBT photodetector and an NMOSFET, as shown Fig. 1(b). The proposed APS excluded the GBT photodetector, which was included in the previous WDR APS structure. The structures were very similar, with one important difference, as shown Fig. 1(c). The operation of the GBT photodetector can be described by the flow of carriers. (13,14) The built-in field induced by the gate and p-silicon substrate separates photogenerated electron-hole pairs. Holes drift toward the channel and are swept into the sensing node of the pixel. On the other hand, electrons accumulate in the body. These accumulated electrons reduce the potential barrier of the holes flowing from the source to the sensing node in the pixel and reduce the feedback to the gate through the gate/body connection, which acts as a negative gate voltage. Thus, the photodetector has high sensitivity because the photocurrent is highly amplified. The output signal of the pixel increases owing to the accumulated holes in the sensing node.

# 2.2 Feedback mechanism of proposed APS

The gate of  $M_4$  is connected to a source follower in the proposed APS to enable feedback. Under low illumination conditions,  $M_4$  is under the subthreshold region. After a certain charge accumulation period,  $M_4$  is gradually turned on because of the increased output voltage, which

Fig. 1. (Color online) Schematic diagrams of (a) conventional APS with GBT photodetector, (b) previous WDR APS, and (c) proposed APS.

is connected to the gate of  $M_4$ . During this time, the sensitivity slope is decreased owing to the feedback current of  $M_4$ . When a positive voltage is applied to the gate relative to the source voltage of  $M_4$ , negative charges are induced in the underlying gate of  $M_4$  by the formation of a depletion region and a thin surface region containing mobile electrons. These induced electrons form the channel of  $M_4$  and allow feedback current to flow from the source to the drain. There is a significant amount of current flow from the source to the drain of  $M_4$ . Therefore, the sensitivity of the proposed pixel decreases and the saturation of the sensing node is delayed, so that the dynamic range can be extended. Moreover, the feedback circuit would automatically control the amount of charges under high illumination conditions to delay the sensing node saturation by applying a reference voltage.

# 3. Results and Discussion

#### 3.1 Simulation results

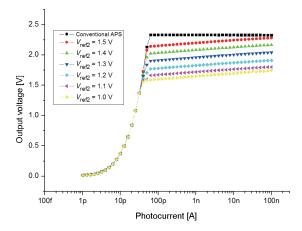

The body of the GBT photodetector is connected to the floating gate that significantly amplifies the photocurrent. It exhibits a higher responsivity than a conventional p-n junction photodiode. Therefore, the conventional APS with the GBT photodetector has a narrow dynamic range. Figure 2 shows the output voltages of the conventional APS and proposed APS plotted against

Fig. 2. (Color online) Simulation results of the variation of the conventional APS with GBT photodetector and the output voltage in the proposed APS as a function of  $V_{ref2}$ .

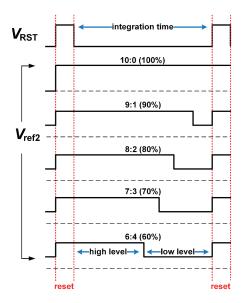

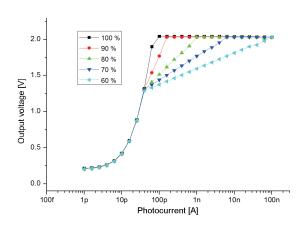

the photocurrent when the integration time is 100 µs. The conventional APS with the GBT photodetector is saturated at approximately 70 pA, with high sensitivity and linear response, as shown in Fig. 2. However, the proposed APS is still not saturated at 100 nA, as shown in Fig. 2. This means that the dynamic range is increased under high illumination conditions. The reason for the WDR operation of the proposed APS is that it has high sensitivity at a low illumination level, whereas it exhibits low sensitivity at a high illumination level according to the feedback MOSFET  $M_4$ . The voltage level of  $V_{ref2}$  can control the dynamic range of the proposed APS, as shown in Fig. 2. This is similar to previous works, wherein APS was previously unable to adjust the dynamic range. (14-16) In the case of the proposed APS, the dynamic range can easily be adjusted by varying the reference voltage level. In addition, the proposed APS can control the dynamic range by adjusting the duration in which the reference voltage is applied. Figure 3 shows the timing diagram of the control signals. The proposed APS operation consists of three phases, namely, the reset phase, the high- $V_{\rm ref2}$  phase, and the low- $V_{\rm ref2}$  phase. The voltage  $V_{\rm rst}$  is changed from  $V_{\rm SS}$  to  $V_{\rm DD}$  at the reset phase. Now,  $M_1$  is OFF and the photodetector starts the integration. At the high- $V_{\text{ref2}}$  phase, the output voltage of the proposed APS increases linearly. At the low- $V_{\text{ref2}}$  phase,  $M_4$  is gradually turned on, and the output voltage increases logarithmically. During that time, the slope of the output voltage changes owing to the feedback current. Thus, in the proposed APS, a variable dynamic range is achieved by adjusting the low- $V_{ref2}$  phase. Figure 4 shows the output voltage of the proposed APS with photocurrent as a function of control signal. According to the ratio of the high- $V_{ref2}$  phase to the low- $V_{ref2}$  phase, the proposed APS exhibits variable sensitivity in the logarithmic region by adjusting the duration of the low- $V_{ref2}$  phase.

## 3.2 Measurement results

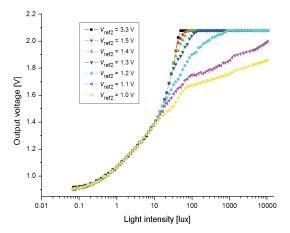

Figure 5 shows the measurement results of the variation of the output voltage in the proposed APS as a function of  $V_{\text{ref2}}$ . These results are similar to the simulation results, as shown Fig. 2. In common with a previous work, (13-16) the proposed pixel can choose the operating mode on the basis

Fig. 3. (Color online) Timing diagram of the control signals for WDR as a function of duty cycle of  $V_{\text{ref2}}$ .

Fig. 4. (Color online) Simulation results of the variation of the output voltage in the proposed APS as a function of  $V_{\rm ref2}$  duty cycle.

Fig. 5. (Color online) Measurement results of the variation of the output voltage in the proposed APS as a function of  $V_{\text{ref2}}$ .

of the reference voltage. When  $V_{\rm ref2}$  is 3.3 V, the proposed pixel was operated in the conventional mode, because  $\rm M_4$  was not working. When  $V_{\rm ref2}$  is at another level, the proposed pixel was operated in the WDR mode. When the proposed pixel was operated in the normal mode, the output voltage was saturated with a high sensitivity at 30 lux because the feedback circuit was disabled by  $V_{\rm ref2}$ . On the other hand, when the proposed pixel was operated in the WDR mode, the slope of the output voltage was changed over 20 lux. Therefore, the level of  $V_{\rm ref2}$  can control the dynamic range of the proposed APS. Thus, the dynamic range of the proposed APS was varied by adjusting the reference voltage level.

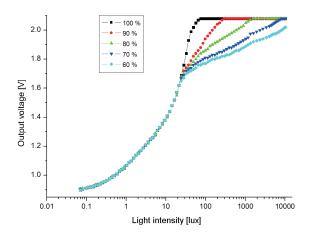

Figure 6 shows the measurement results of the variation of the output voltage in the proposed APS as a function of the duty cycle of  $V_{\rm ref2}$ . The output voltage of the proposed APS increased linearly in the high- $V_{\rm ref2}$  phase. The slope of the output voltage changed logarithmically in the low- $V_{\rm ref2}$  phase. As shown in Fig. 6, the duty cycle of  $V_{\rm ref2}$  can control the dynamic range of the proposed APS. The proposed APS exhibits 91 dB of the dynamic range for the 6:4 duty cycle of  $V_{\rm ref2}$  (high- $V_{\rm ref2}$  phase:low- $V_{\rm ref2}$  phase) and 54 dB for the 10:0 duty cycle of  $V_{\rm ref2}$ .

A testing chip was designed and fabricated using Magna/SK Hynix 0.35  $\mu$ m 2-poly 4-metal CMOS technology where the size is 13  $\times$  13  $\mu$ m<sup>2</sup>. The overall performance characteristics of the proposed APS structure are summarized in Table 1 and compared with those reported in previous works.

#### 3.3 Discussion

The pixel size of the proposed APS is slightly larger than that of the conventional APS with a GBT photodetector because of the additional NMOSFET used. However, the dynamic range of the proposed APS is considerably wider than that of a conventional APS with a GBT photodetector. In

Fig. 6. (Color online) Measurement results of the variation of the output voltage in the proposed APS as a function of  $V_{\text{ref2}}$  duty cycle.

Characteristics of previously reported and proposed APSs.

|                | 1 2 1                    | 1 1                          |                                                   |

|----------------|--------------------------|------------------------------|---------------------------------------------------|

| Features       | Previous work(13)        | Previous work(16)            | Proposed APS                                      |

| Process        | 0.35 μm CMOS             | 0.35 μm CMOS                 | 0.35 μm CMOS                                      |

| Supply voltage | 3.3 V                    | 3.3 V                        | 3.3 V                                             |

| Pixel size     | $10 \times 10 \ \mu m^2$ | $13.6 \times 13.6 \ \mu m^2$ | $13 \times 13 \ \mu m^2$                          |

| Detector       | GBT photodetector        | two GBT photodetectors       | GBT photodetector                                 |

| Fill factor    | 37.2%                    | 14%                          | 15.3%                                             |

|                |                          |                              | $V_{\text{ref2}} = 3.3 \text{ V} : 43 \text{ dB}$ |

|                |                          |                              | $V_{\text{ref2}} = 1 \text{ V} : 97 \text{ dB}$   |

| Dynamic range  | 28 dB                    | Normal mode: 28 dB           | 10:0 duty cycle: 54 dB                            |

|                |                          | WDR mode: 98 dB              | 6:4 duty cycle: 91 dB                             |

addition, the dynamic range of the proposed APS is tunable by adjusting the level of the reference voltage and the duty cycle of the reference voltage. Therefore, the proposed AP might be useful for wide-dynamic-range CMOS image sensor applications.

In comparison with the conventional APS using a pinned photodiode, the proposed APS exhibits a rather large dark noise of 12.69 mV<sub>rms</sub> because of current-amplifying characteristics of the GBT detector. (15) Reset noise can be eliminated by applying a noise reduction method such as the double sampling (DS) circuit or correlated double sampling (CDS) circuit method. Besides, the lin-log pixel has a knee point variation causing image degradation. We will optimize the proposed pixel and focus on research reducing the knee point variation.

## 4. Conclusions

In this study, we proposed a novel CMOS image sensor to extend the dynamic range by means of output voltage feedback. The proposed APS was designed and fabricated using a  $0.35~\mu m$  2-poly 4-metal standard CMOS process. The pixel size of the proposed APS is slightly larger than that of a conventional APS with a GBT photodetector because of the additional NMOSFET used. However, the dynamic range of the proposed APS is considerably wider than that of a conventional APS with a GBT photodetector. In addition, the dynamic range of the proposed APS is tunable from a minimum of 43 dB (160%) to a maximum of 97 dB (360%) by adjusting the reference voltage. Control of the dynamic range is easier in the case of the proposed APS compared with other reported methods.

# Acknowledgements

This work was supported by the following: National Research Foundation of Korea (NRF) funded by the Korea government (MSIP) (Grant No. 2008-0062617), Samsung Electronics Co., Ltd., BK21 Plus project funded by the Ministry of Education, Korea (Grant No. 21A20131600011), and the Integrated Circuit Design Education Center (IDEC), Korea.

### References

- 1 A. J. P. Theuwissen: IEEE Solid-State Circuits Magazine 2 (2010).

- 2 C. Graf, T. Harendt, C. Engelhardt, C. Scherjon, K. Warkentin, H. Richter, and J. N. Burghartz: IEEE J. Solid-State Circuits 44 (2009) 281.

- 3 H. Cheng, B. Choubey, and S. Collins: IEEE Trans. Electron Devices 56 (2009) 2423.

- 4 W.-J. Liu, H.-F. Yeh, and O. T.-C. Chen: Midwest Symposium on Circuits and Systems 1 (2005) 384.

- 5 Y. Chae, K. Cho, B. Kim, and G. Han: IEEE Electron Device Lett. 28 (2007) 495.

- 6 W. Lee, N. Akahane, S. Adachi, K. Mizobuchi, and S. Sugawa: IEEE Electron Devices 56 (2009) 2436.

- 7 D. Park, J. Rhee, and Y. Joo: IEEE Electron Device Lett. 28 (2007) 890.

- 8 M. Ikebe and K. Saito: IEEE Sens. J. 7 (2007) 897.

- 9 W. Lee, N. Akahane, S. Adachi, K. Mizobuchi, and S. Sugawa: IEEE Electron Devices 56 (2009) 2436.

- 10 J. H. Park, S. Kawahito, and Y. Wakamori: IEICE Electron. Express 2 (2005) 482.

- 11 G. Storm, R. Henderson, J. E. D. Hurwits, D. Renshaw, K. Findlater, and M. Purcell: IEEE J. Solid-State Circuits 41 (2006) 2095.

- 12 B. Choubey and S. Collins: IEEE Sens. J. 7 (2007) 1066.

- 13 S.-H. Seo, S.-H. Lee, M.-Y. Do, J.-K. Shin, and P. Choi: Jpn. J. App. Phys. 45 (2006) 3470.

- 14 S.-H. Seo, K.-D. Kim, M.-Y. Seo, J.-S. Kong, J.-K. Shin, and P. Choi: Sens. Mater. 19 (2007) 435.

- 15 H.-Y. Hyun, J.-S. Kong, and J.-K. Shin: Sens. Mater. **20** (2008) 381.

- 16 M. Bae, S.-H. Jo, M. Lee, J.-Y. Kim, J. Choi, P. Choi, and J.-K. Shin: J. Sens. Sci. Technol. 21 (2012) 413.