S & M 1973

# Design of Planar Si Thermoelectric Generators with Phononic Crystal Patterning

Masahiro Nomura,<sup>1,2\*</sup> Ryoto Yanagisawa,<sup>1</sup> Peter Zimmermann,<sup>1</sup> Patrick Ruther,<sup>3</sup> and Oliver Paul<sup>3</sup>

<sup>1</sup>Institute of Industrial Science, The University of Tokyo,

4-6-1, Komaba, Meguro-ku, Tokyo 153-8505, Japan

<sup>2</sup>PRESTO, Japan Science and Technology Agency,

4-1-8, Honcho, Kawaguchi-si, Saitama 332-0012, Japan

<sup>3</sup>Microsystem Materials Laboratory, Dept. of Microsystems Eng. (IMTEK),

University of Freiburg, Georges-Koehler-Allee 103, D-79110 Freiburg, Germany

(Received January 15, 2019; accepted January 31, 2019)

**Keywords:** thermoelectrics, energy harvesting, phonon, phonon engineering, silicon

This paper presents the design and optimization of planar poly-Si thermoelectric generators (TEGs) for energy harvesting application. Temperature and electric potential distributions are simulated using material parameters, which were experimentally obtained from test structures, by the finite element method to evaluate the performance of TEGs. TEGs with unpatterned membranes or membranes with phononic crystal (PnC) nanostructures are investigated to evaluate the increase in power density by nanopatterning. The power density is increased by PnC nanopatterning with larger holes and the optimal bridge length decreases owing to a higher thermal resistance. The series of simulations shows that nanopatterning increases the power density 2.5 times at a smaller bridge length and is also advantageous from the viewpoint of mechanical strength.

### 1. Introduction

The concept of smart dust, which was followed by the internet of things (IoT) and ubiquitous computing, has been waiting for advanced technologies including energy harvesting for practical use in society for more than two decades. Thermoelectrics is one of the promising energy conversion technologies to realize an energy autonomous wireless sensor node for this purpose. Various thermoelectric materials were developed and their thermoelectric properties were investigated. Silicon (Si) is the most practical material in electronics, but not for thermoelectric application at room temperature owing to its very high thermal conductivity. However, researchers found that thermal conduction in nanostructures is much lower than in bulk and can be dramatically reduced by nanostructuring. This is due to the enhancement of diffusive surface scattering, and the figure of merit ZT can be as high as 0.6 at room temperature in nanowires. We investigate thermal phonon transport and heat conduction in

<sup>\*</sup>Corresponding author: e-mail: nomura@iis.u-tokyo.ac.jp https://doi.org/10.18494/SAM.2019.2297

nanostructured Si membranes, especially in membranes with PnC nanostructures, and develop planar Si thermoelectric devices. A planar Si thermoelectric device can be fabricated using CMOS and micro-electromechanical system (MEMS) technologies, and is suitable for low-cost mass production. In addition, the high reliability and environmental friendliness of Si are also advantageous for its widespread use in the environment and society. However, a planar device requires careful thermal design to generate sufficient electric power to drive microelectronic devices, because the temperature difference between the edges of a bridge structure of a thermoelectric membrane is normally small. Xie *et al.* designed and fabricated devices with peripheral cavity structures formed by CMOS and MEMS processes, and reported their high performance. We also fabricate planar devices but with nanostructuring in Si membranes to increase the thermal resistance, which results in higher power generation.

In this work, we report the design and simulated performance of planar Si thermoelectric devices with PnC nanostructures at room temperature based on parameters experimentally obtained using test structures. A thermal analysis was performed by the finite element method for various bridge lengths for optimization. We also investigated the importance of a substrate and compared the maximum power density at the optimum bridge length.

## 2. Simulation and System

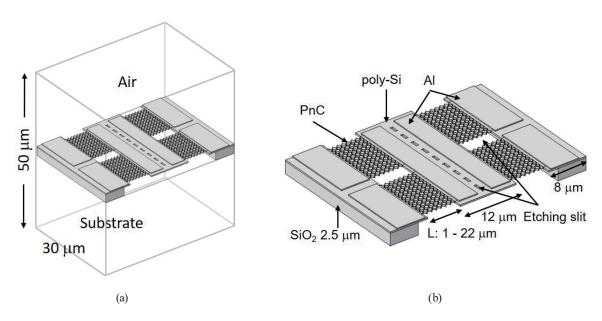

In this section, the simulated structures and details of the simulation are explained. A three-dimensional model  $[50 \times 30 \times (30-72)]$  µm<sup>3</sup> was built as shown in Fig. 1(a). The simulated system is composed of device [Fig. 1(b)], air, and substrate parts. The boundary condition in the in-plane directions is periodic, but the upper plane of the air part and the bottom plane of the substrate part were fixed and their temperature difference ( $\Delta T_{env}$ ) was set at 10 K. In this simulation, the substrate was heated and heat escaped to the air via gas-solid heat exchange with natural convection. The thermal analysis in the solid was based on the diffusive model using Eq. (1) with the density  $\rho$  and heat capacity  $C_p$ ,

$$\rho C_p \partial T / \partial t = \kappa \nabla^2 T. \tag{1}$$

The details and dimensions of the device part are shown in Fig. 1(b). Two pairs of n- and p-type poly-Si thermoelectric generators are fabricated on a SiO<sub>2</sub> sacrificial layer and connected by Al electrodes. PnC nanostructures are formed in the bridges and function as thermoelectric materials. Etching slits are formed in the central island part to isolate it from the substrate. The width of the bridge is 12 μm and the widths of the Al electrodes in the central island and on SiO<sub>2</sub> are 4 and 6 μm, respectively. The thicknesses of the poly-Si, Al electrode, SiO<sub>2</sub>, air box, and substrate are 300 nm, 200 nm, 2.5 μm, 25 μm, and 25 μm, respectively. The material and other parameters are summarized in Table 1. Thermal analysis was performed by the finite element method for unpatterned membranes and membranes with PnCs with circular airholes with radii of 60, 100, and 120 nm. Each PnC has arrays of through holes aligned as a square lattice with a periodicity *a* of 300 nm in the suspended membrane. The electrical conductivity

Fig. 1. (a) Schematic of the simulated system. (b) Details of the central part of the thermoelectric material with PnC patterning and Al electrodes.

Table 1

Parameters for n- and p-type poly-Si layers and the device used in the simulation.

| Values for                  | Membrane    | PnC, r = 60  nm | PnC, r = 100  nm | PnC, $r = 120 \text{ nm}$ |

|-----------------------------|-------------|-----------------|------------------|---------------------------|

| n-type/p-type               |             | (r/a = 0.2)     | (r/a = 0.33)     | (r/a = 0.4)               |

| σ (kS/m)                    | 84/20       | 78/15           | 72/15            | 70/14                     |

| κ (W/mK)                    | 11/18       | 4.0/8.7         | 2.5/7.5          | 2.0/7.2                   |

| $S(\mu V/K)$                | -80/240     |                 |                  |                           |

| ZT at 300 K                 | 0.015/0.019 | 0.037/0.030     | 0.055/0.035      | 0.067/0.034               |

| $R_{cont} (\Omega \mu m^2)$ | 123/95      |                 |                  |                           |

$\sigma$ , thermal conductivity  $\kappa$ , and Seebeck coefficient S were taken from our previous work, (14) and  $R_{cont}$  was taken from the literature. (20)

#### 3. Simulation Results and Discussion

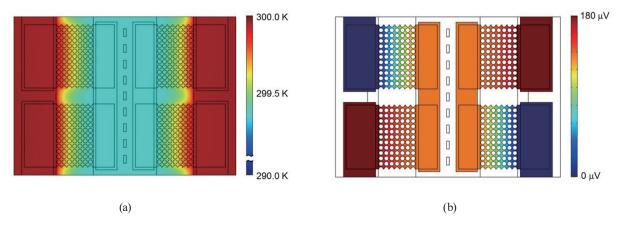

Temperature and electric potential distributions in the device part were simulated at an environmental temperature difference  $\Delta T_{env}$  of 10 K (Fig. 2). The temperature distribution simulated for a structure with a PnC structure with airholes of r=120 nm is shown in Fig. 2(a). The poly-Si part on the SiO<sub>2</sub> layer is hotter and the suspended central island is cooler, but the temperature difference between edges of the suspended thermoelectric material,  $\Delta T_{mat}$ , is only 560 mK, which is only about 6% of  $\Delta T_{env}$ . However,  $\Delta T_{mat}$  is increased 3.2 times by PnC nanopatterning compared with the increase for an unpatterned membrane at the bridge length L=7 µm.

Fig. 2. (Color online) Examples of simulated (a) temperature and (b) electrical potential distributions in the thermoelectric device at  $\Delta T_{env} = 10$  K. The upper left and lower right bridges are p-type Si.

This finding indicates that the thermal design is very important for a planar device and emphasizes the importance of the high thermal resistance of the bridges. The simulation also gives the electrical potential distribution shown in Fig. 2(b). One pair of n- and p-type thermocouples generates 180  $\mu$ V. The p-type Si bridge generates a higher thermoelectric voltage than the n-type Si bridge owing to its larger Seebeck coefficient. The open-circuit output voltage  $V_0$  is given by  $V_0 = (|S_n| + S_p) \Delta T_{mat}$ , where  $S_n$  and  $S_p$  are the Seebeck coefficients for the n- and p-type poly-Si membranes, respectively.

The output power  $P_0$  was estimated for unpatterned and PnC-nanopatterned membranes using various bridge lengths to optimize at a fixed bridge width of 12  $\mu$ m.  $P_0$  was calculated with load resistance given by the internal electrical resistance of one unit,  $R_{total}$ , and  $P_0$  is given by

$$P_0 = \frac{V_0^2}{4R_{total}} = \frac{|S_n| + S_p}{4R_{total}} \Delta T_{mat}^2.$$

(2)

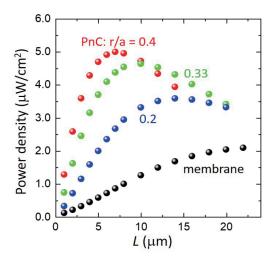

Figure 3 shows the length dependence of the power density. When the bridge is short,  $\Delta T_{mat}$  is low owing to a low thermal resistance. As the bridge becomes longer,  $\Delta T_{mat}$  saturates and the foot print of one unit becomes unnecessarily large. Therefore, an optimum bridge length exists and continuously decreases as the thermal resistivity of the bridge increases, i.e., for a PnC nanostructure with larger holes. The maximum power density is increased 2.5 times by PnC patterning. This increase mainly stems from a larger  $\Delta T_{mat}$  and an increased ZT, both of which result from thermal conductivity reduction by nanopatterning. In addition, a shorter bridge is better for practical use in a harsh environment because the bridge is mechanically more robust. Therefore, nanopatterning is an effective approach for improving the performance of a planar thermoelectric device as long as the process cost is low. The nanoholes used in this study are large enough to be fabricated by nanoimprint lithography, which enables low-cost large-area patterning.

Fig. 3. (Color online) Simulated power densities at various bridge lengths (*L*) for TEGs with unpatterned membranes or membranes PnC-nanopatterned with different circular hole radii.

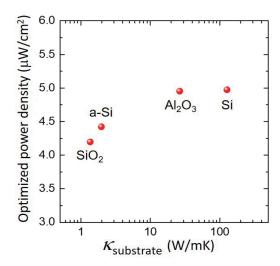

Fig. 4. (Color online) Calculated power density at each optimum bridge length with different substrates.

Finally, we investigated the importance of the substrate in the thermal design. As the thermal conductivities ( $\kappa_{substrate}$ ) of the substrate, 1.38, 2, 27, and 130 W/mK were used as the values of SiO<sub>2</sub>, amorphous Si (a-Si), Al<sub>2</sub>O<sub>3</sub>, and single-crystalline Si, respectively. Figure 4 shows that a higher power density is achieved with a thermally more conductive substrate. This is because a higher thermal gradient is formed in the thermoelectric material. It is also found that the power density does not change markedly above  $\kappa_{substrate} \sim 10$  W/mK. This conclusion is also valid for a 500- $\mu$ m-thick standard substrate. This is a useful finding because the substrate may not necessarily be thermally highly conductive, and thus low-cost ceramics can also be used as substrates.

#### 4. Conclusions

Planar poly-Si thermoelectric devices were designed and their performance at room temperature was investigated by thermal analysis using the finite element method. The thermal design to increase the temperature difference between the edges of a suspended thermoelectric material is very important for the enhancement of power generation. PnC patterning with a periodicity of 300 nm reduces the thermal conductivity and results in a ZT improvement and a 2.5-fold power generation enhancement. The analysis also indicates that the substrate does not necessarily have to be thermally conductive; a low-cost substrate with a moderate thermal conductivity is available. The nanopatterning of a thermoelectric material by a low-cost and large-area fabrication process is a practical approach for obtaining high-performance planar thermoelectric devices.

# Acknowledgments

This work was supported by Kakenhi Japan Society for the Promotion of Science (15K13270 and 17H02729), PRESTO, Japan Science and Technology Agency (JPMJPR15R4), Maeda Corporation, and Toppan Printing.

#### References

- 1 G. J. Snyder and E. S. Toberer: Nat. Mater. 7 (2008) 105. https://doi.org/10.1038/nmat2090

- 2 E. S. Toberer, A. Zevalkink, and G. J. Snyder: J. Mater. Chem. 21 (2011) 15843. https://doi.org/10.1039/cljm11754h

- 3 T. Zhu, Y. Liu, C. Fu, J. P. Heremans, J. G. Snyder, and X. Zhao: Adv. Mater. 29 (2017) 1605884. https://doi.org/10.1002/adma.201605884

- 4 L. Weber and E. Gmelin: Appl. Phys. A 53 (1991) 136. https://doi.org/10.1007/BF00323873

- 5 K. Esfarjani, G. Chen, and H. T. Stokes: Phys. Rev. B 84 (2011) 085204. https://doi.org/10.1103/ PhysRevB.84.085204

- 6 M. S. Dresselhaus, G. Chen, M. Y. Tang, R. G. Yang, H. Lee, D. Z. Wang, Z. F. Ren, J.-P. Fleurial, and P. Gogna: Adv. Mater. 19 (2007) 1043. https://doi.org/10.1002/adma.200600527

- 7 P. Pichanusakorn and P. Bandaru: Mater. Sci. Eng., R 67 (2010) 19. https://doi.org/10.1016/j.mser.2009.10.001

- 8 J. Tang, H.-T. Wang, D. H. Lee, M. Fardy, Z. Huo, T. P. Russell, and P. Yang: Nano Lett. 10 (2010) 4279. https://doi.org/10.1021/n1102931z

- 9 L. Yang and A. J. Minnich: Sci. Rep. 7 (2017) 44254. https://doi.org/10.1038/srep44254

- 10 J. Lim, H. T. Wang, J. Tang, S. C. Andrews, H. So, J. Lee, D. H. Lee, T. P. Russell, and P. Yang: ACS Nano 10 (2016) 124. https://doi.org/10.1021/acsnano.5b05385

- 11 A. I. Hochbaum, R. Chen, R. D. Delgado, W. Liang, E. C. Garnett, M. Najarian, A. Majumdar, and P. Yang: Nature 451 (2008) 163. https://doi.org/10.1038/nature06381

- 12 A. I. Boukai, Y. Bunimovich, J. Tahir-Kheli, J.-K. Yu, W. A. Goddard III, and J. R. Heath: Nature **451** (2008) 168. https://doi.org/10.1038/nature06458

- 13 M. Nomura, J. Nakagawa, Y. Kage, J. Maire, D. Moser, and O. Paul: Appl. Phys. Lett. 106 (2015) 143102. https://doi.org/10.1063/1.4917036

- 14 M. Nomura, Y. Kage, D. Müller, D. Moser, and O. Paul: Appl. Phys. Lett. 106 (2015) 223106. https://doi. org/10.1063/1.4922198

- 15 J. Nakagawa, Y. Kage, T. Hori, J. Shiomi, and M. Nomura: Appl. Phys. Lett. 107 (2015) 023104. https://doi. org/10.1063/1.4926653

- 16 R. Anufriev, J. Maire, and M. Nomura: Phys. Rev. B 93 (2016) 045411. https://doi.org/10.1103/ PhysRevB.93.045411

- 17 R. Yanagisawa, J. Maire, A. Ramiere, R. Anufriev, and M. Nomura: Appl. Phys. Lett. **110** (2017) 133108. https://doi.org/10.1063/1.4979080

- 18 M. Strasser, R. Aigner, M. Franosch, and G. Wachutka: Sens. Actuators, A Phys. 97–98 (2002) 535. https://doi. org/10.1016/S0924-4247(01)00815-9

- 19 A. P. Perez-Marín, A. F. Lopeandía, L. Abad, P. Ferrando-Villaba, G. Garcia, A. M. Lopez, F. X. Muñoz-Pascual, and J. Rodríguez-Viejo: Nano Energy 4 (2014) 73. https://doi.org/10.1016/j.nanoen.2013.12.007

- 20 J. Xie, C. Lee, M.-F. Wang, Y. Liu, and H. Feng: J. Micromech. Microeng. **19** (2009) 125029. https://doi.org/10.1088/0960-1317/19/12/125029

- 21 J. Xie, C. Lee, and H. Feng: J. Microelectromech. Syst. 19 (2010) 317. https://doi.org/10.1109/ JMEMS.2010.2041035

#### **About the Authors**

Masahiro Nomura is an associate professor in the Institute of Industrial Science, The University of Tokyo. He received his bachelor, master, and Ph.D. degrees in applied physics in 2000, 2002, and 2005, respectively, from The University of Tokyo. His research interests include hybrid quantum science, phonon/heat transport in semiconductor nanostructures, and energy harvesting by thermoelectrics. The concept of his current research is "from photonics to phononics" using phononic crystals, which have some physical analogy with photonic crystals. He is a recipient of The Young Scientists' Prize by the Minister of Education, Culture, Sports, Science and Technology (2012), ISCS Young Scientist Award (2017), German Innovation Award – Gottfried Wagener Prize (2018), and ten other awards. (nomura@iis.u-tokyo.ac.jp)

**Ryoto Yanagisawa** received his B.E. degree from Keio University, Japan, in 2015 and his M.E. degree from the University of Tokyo, Japan, in 2017 where he is currently a Ph.D. student. His research interests are physics for heat transport in nanostructured semiconductor materials and its application to thermoelectric energy harvesters. (r-yanagi@iis.u-tokyo.ac.jp)

**Peter Zimmermann** received his B.Sc. and M.Sc. degrees in microsystems engineering from the University of Freiburg, Germany, in 2015 and 2017 respectively. From 2018 onwards, he is an analog design engineer at Infineon Technologies, Germany. (Peter.Zimmermann-EE@infineon.com)

Patrick Ruther studied physics and received the Ph.D. degree in mechanical engineering in 1996. Between 1996 and 1998, he was PostDoc at the Research Center Karlsruhe, Germany, developing LIGA-based microoptical components. Since October 1998, he is a senior scientist in the Department of Microsystems Engineering (IMTEK), University of Freiburg. His focus is on the design, fabrication, and characterization of CMOS-compatible MEMS devices including microoptical functionality for biomedical applications, e.g., neuroscience and optogenetics. He coordinated the EU project NeuroSeeker targeting the next generation of neural probes comprising electronic and optical functionalities, and is a member of the BrainLinks-BrainTools Cluster of Excellence at the University of Freiburg. He is a cofounder of the spin-off company ATLAS Neuroengineering, Belgium.

Oliver Paul received his Diploma (Physics) and Ph.D. degrees from ETH Zürich, Switzerland, in 1986 and 1990, respectively. From 1990 to 1998, he has held postdoctoral, group leader and lecturer positions at the Fraunhofer Institute for Solar Energy Research in Freiburg Germany, and at ETH Zürich. Since 1998, he has been a professor, the director of the Department of Microsystems Engineering and the dean of the Faculty of Engineering at the University of Freiburg. He is an initiator and member of the Cluster of Excellence BrainLinks-BrainTools and has co-founded the companies Sensirion AG and Atlas Neuroengineering. His research interests are in microfabrication technology, MEMS for neuroscience, and semiconductor microsensors from their foundations to calibration.

(paul@imtek.uni-freiburg.de)